ANDOVER, MA., March 22, 2012 – Avery Design Systems Inc., an innovator in functional verification productivity solutions, today announced availability of its revolutionary X verification solution, SimXACT, targeting comprehensive X propagation analysis including gate-level X pessimism analysis and automatic correction of gate-level simulation results, and XVER, X optimism analysis of RTL simulation.

The inherent limitations of handling non-determinism associated with X values in logic simulation means simulation results may not reflect actual hardware operation. Insight XVER uses formal methods to accurately analyze X propagations enabling engineers to:

– Run gate-level simulations free of X pessimism issues

– Diagnose occurrences of X optimism in RTL simulations alerting designers who may be unaware of potential non-deterministic sequential behaviors

– Perform sequential X propagation forward and backward tracing and debug

– Accurately analyze and report X states during hardware reset and power transition sequences to confirm design specs

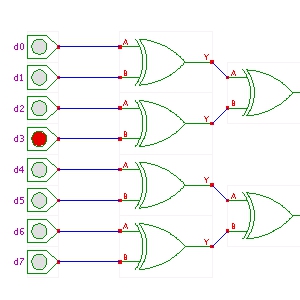

SimXACT utilizes a hybrid method to perform formal combinatorial X pessimism analysis while running gate-level simulation of a full chip netlist. SimXACT supports Cadence NC-Sim, Synopsys VCS, and Mentor Questa. When an X is encountered during simulation at a register/latch input or chip-level output, SimXACT formally proves whether the X is real or false. If false, Insight applies its patent pending technology to dynamically correct the simulation value on the fly in the simulator as well as generates HDL code pinpointing a force/release at the origin of the X pessimism. The set of HDL fixes can be used for subsequent simulations which run at their native, full simulation speed and are free of X pessimism. SimXACT also identifies clocking issues associated with internal clock generators and gated clocks and generates forces for them. Real X propagation can be debugged using a full sequential backtrace report showing the exact register to register paths from original X source registers or inputs to their destination registers spanning multiple clock cycles.

“If you’ve ever had to debug X propagation issues in failing gate-level simulations you know how cumbersome and time consuming it can be especially when the Xs turn out to be false due to a limitation of Verilog simulators known as X pessimism. Developing manual force/release fixes or applying random 0/1 deposit to registers at X are less than ideal solutions because bugs may be masked. SimXACT has been used analyze and correct chip-level simulations in just a few hours which involved 100s of X pessimism occurrences and is guaranteed not to mask any bugs. SimXACT improves design reliability and the automated process eliminates schedule risk during chip signoff.” says Chilai Huang, president of Avery.

XVER supports formal sequential X propagation analysis at the RT-level including X optimism analysis of RTL simulations. Here XVER performs symbolic simulation of actual simulation testcases and analyzes them for the presence of X optimism which will result in non-deterministic sequential design operation. A full sequential backtrace report is generated showing the exact RTL path from original X source registers or inputs to their destination registers spanning multiple clock cycles. Designers can then confirm whether the X propagations are acceptable, eliminate undesirable X sources, or make their design more tolerant of handling the non-determinism. RT-level analysis helps resolve X issues that currently may not be found until gate-level simulation is run.

SimXACT and XVER are part of the Insight product family of innovative automatic formal solutions including

- PSYN – automatic microarchitecture-level property and coverage synthesis addressing the needs of RTL designers to improve baseline coverage metrics and their use of assertion-based verification methods

- DFT – RT-level at-speed DFT testability analysis and automated testpoint insertion to improve small delay defect, transition delay fault (SDD-TDF) and path delay fault scan-based test coverage prior to running ATPG

About Avery Design Systems

Founded in 1999, Avery Design Systems, Inc. enables system and SOC design teams to achieve dramatic functional verification productivity improvements through the use of formal analysis applications for automatic property and coverage generation, X verification, and RT-level DFT at-speed testability analysis; robust core-through-chip-level Verification IP for PCI Express, USB, AMBA, and MIPI standards; and scalable distributed parallel logic simulation. The company is a member of the Synopsys SystemVerilog and VMM Catalyst Programs, Mentor Graphics Modelsim Value Added Partnership (VAP) program, and has established numerous Avery Design VIP partner program affiliations with leading IP suppliers. More information about the company may be found at www.avery-design.com.

For More Information Contact:

Chris Browy

Avery Design Systems

(978) 689-7286

cbrowy@cosmicdawnconsulting.com

KEYWORD: MASSACHUSETTS

INDUSTRY KEYWORD: SOFTWARE COMPUTERS HARDWARE

ELECTRONICS NETWORKING EDA

ELECTRONIC DESIGN AUTOMATION

SOURCE: Avery Design Systems, Inc.