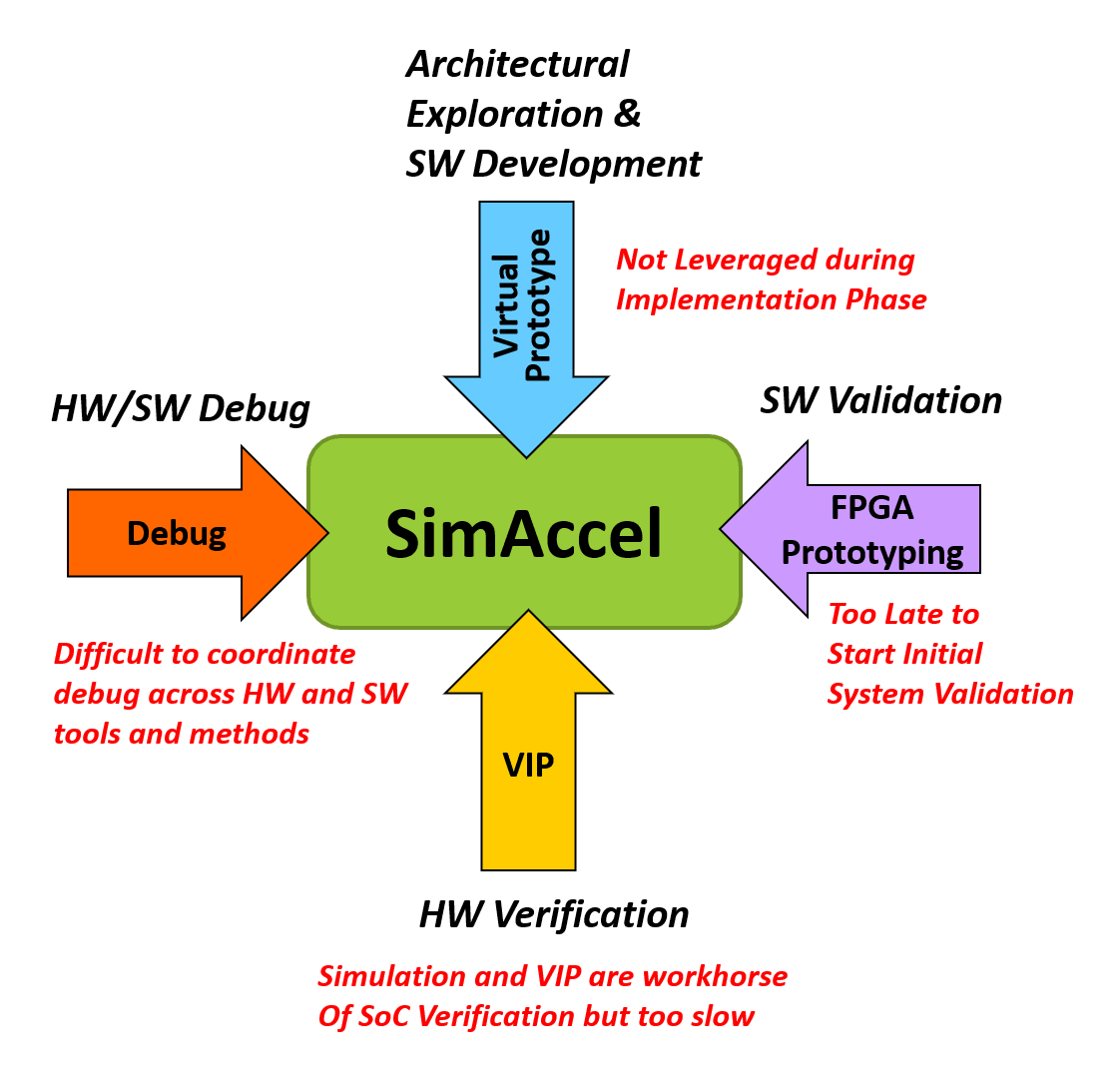

- SimAccel combines advanced technology and methods for a comprehensive verification strategy

- RTL verification using VIP

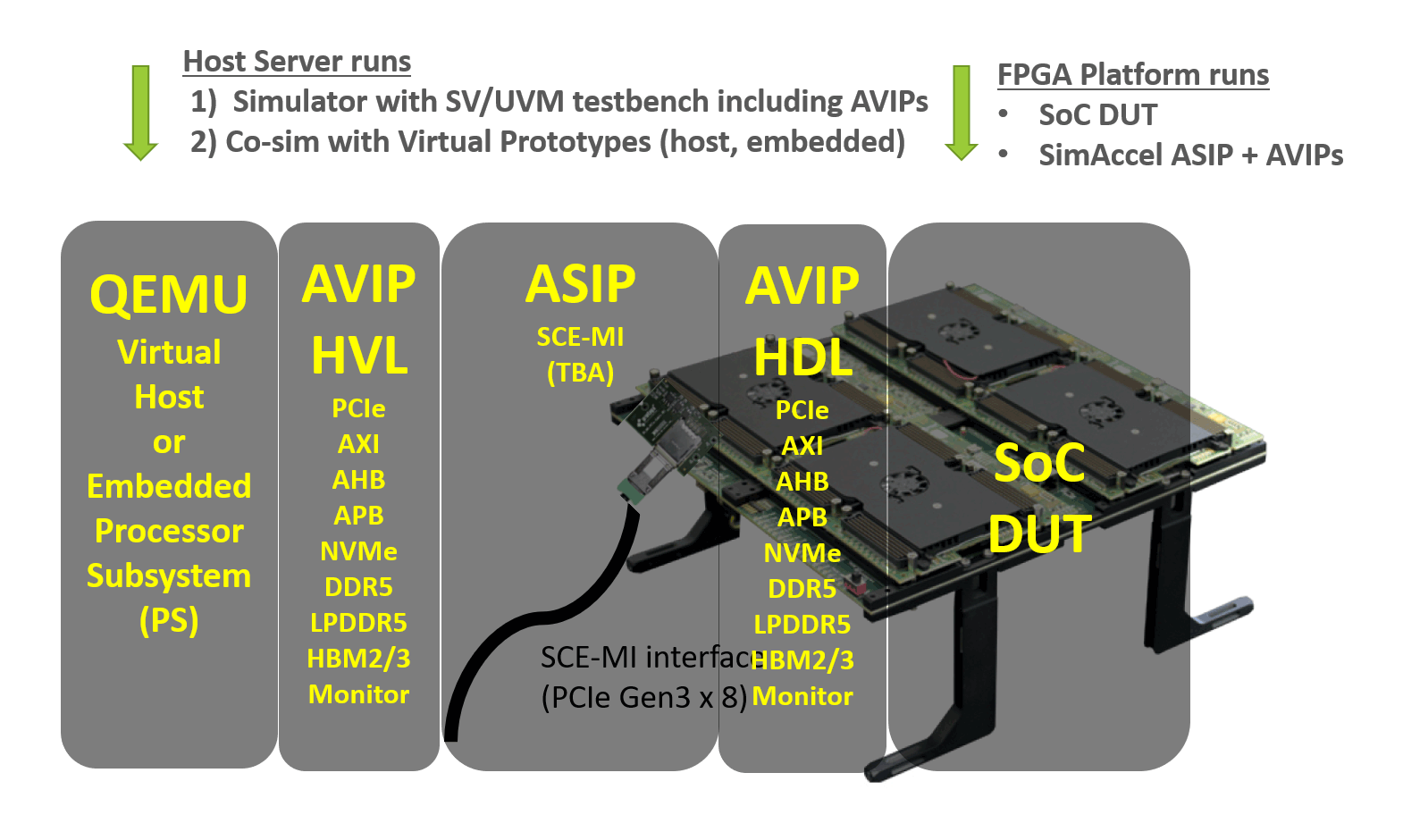

- QEMU Virtual Host and embedded supporting x86, Arm, and RISC-V

- FPGA Prototyping

- Unified HW-SW Debug

- Full suite of Accelerated VIP

- PCIe, CXL, NVMe, DDR/LPDDR/HBM, AMBA, CPI/SFI, PIPE, LPIF

- This allows the creation of domain-specific accelerator solutions

- NVMe

- PCIe/CXL chips (switch, retimer) and IP core-level

SimAccel enables teams to 'Level Up' and 'Go Faster' for Better Productivity and Quality

SimAccel on desktop FPGA prototype system or Xilinx reference boards

FPGA Platforms

- S2C

- proDesign

- Xilinx

- Other multi-FPGA systems

| 440 US+ FPGA | Per Device | Total |

|---|---|---|

| System Logic (K) | 5,541 | 22,164 |

| CLB FF | 5,065 | 20,260 |

| Memory (Mb) | 88 | 354 |

| I/O | 1456 | 1456 |

| DDR4 (GB) | 64 | 512 |

SimAccel Key Features

- Accelerator System IP (ASIP)

- HW/SW Co-emulation IP includes

- HW is synthesized into main FPGA connected to Host PC (includes Xilinx PCIe/XDMA IP)

- Configurable number of AVIP sockets for AMBA and CPI transactors used for DUT or AVIPs

- SV DPI-based SCE-MI SW provides message transport to AXI transactors and utilizes Xilinx XDMA PCIe driver

- Xilinx Vivado FPGA projects for each target FPGA/Board

- HW/SW Co-emulation IP includes

- Accelerated VIPs (AVIPs)

- SV/UVM-based VIP compiled in AVIP mode

- Encrypted, synthesizable RTL/Netlist transactors plug into AXI slots in ASIP

- Leverages commercial IP cores to quality (Mobiveil, Xilinx)

- Enhanced GDB with Embedded HW Debug support for complete HW-SW co-debug

- HW waveform generation support including VCD/FSDB writer

- Automatic Multi-FPGA partitioner software

- Uses standard Vivado-based tool flow for synthesis through implementation

SimAccel NVMe Demo Performance

- Stress test performs 100 random NVMe read and write commands

- Data set varies transfer sizes between 1-2000 LBs/command

- LB size = 4KB

- Transfers range from 4KB – 8MB

- Run more long tests with large transfers (SGLs) on multiple submission queues and VFs

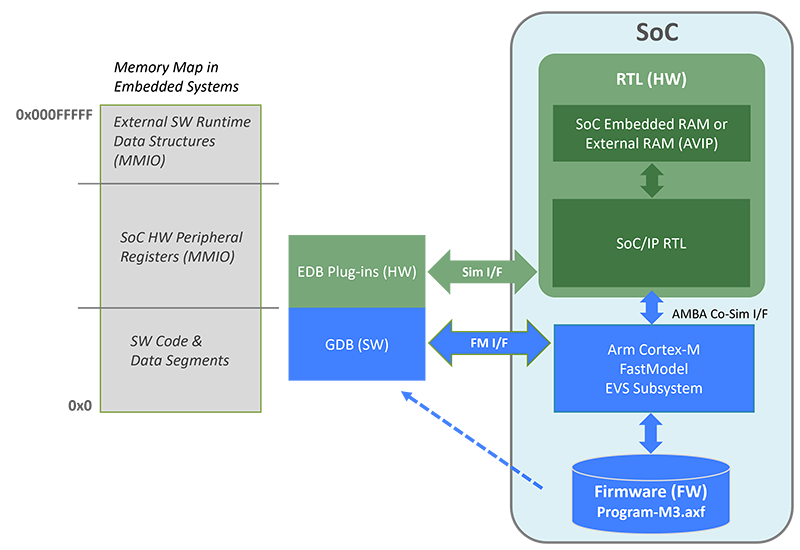

Virtual Prototyping and Co-Emulation, Co-Debug

- Using a single, unified debugger, the hardware and software engineers can carry out effective analysis and debug of the complete design

- HW/SW co-debug is supported through the use of GDB extensions for SimAccel

- Embedded debugging (EDB) commands

- Tightly controls HW and SW execution

- Access complete memory space

- SoC HW peripheral registers and memory (MMIO)

- AVIP embedded protocol trackers display current transactions

- SW callstack and program state

- Control SW and HW execution

- Set breakpoints on HW registers

- Value changes, expressions, error events, or timeouts

- Set breakpoints, watchpoints, catchpoints on SW program

- Program line or state change or expression

- Step program lines, time, clock cycles between

- Set breakpoints on HW registers