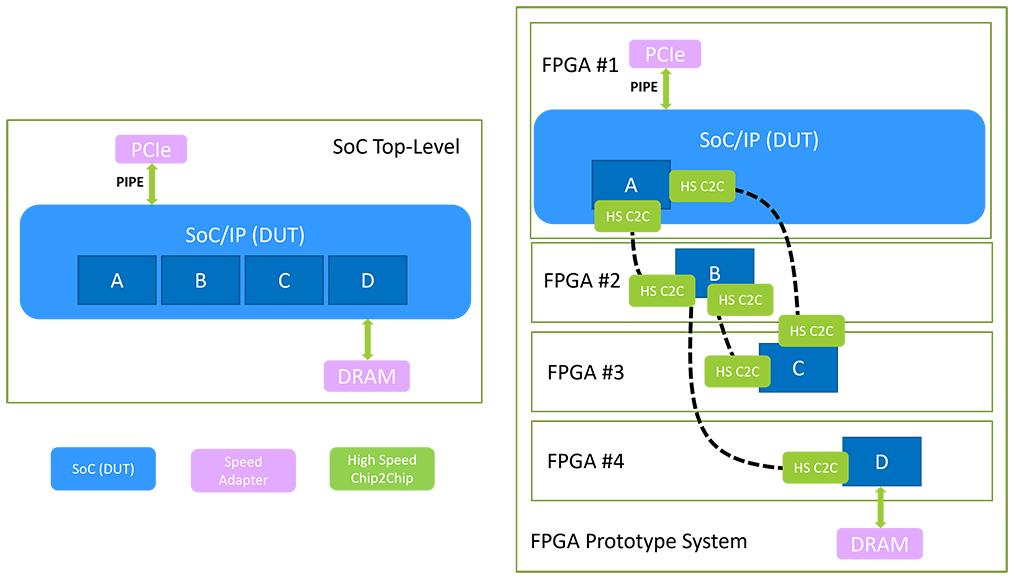

- Multi-FPGA Partitioner – tool enables retargeting SoCs to multiple FPGAs

- PCIe, CLX and USB Speed Adapters – enables running FPGA prototypes on real system platforms running PCIe PCIe, CXL and USB interfaces at native speeds

- Memory Speed Adapter – Speed Adapter enables running FPGA prototype when native memory speed of operation or memory types are not achievable by FPGA prototype systems

Multi-FPGA Partitioner

- Prototyping large SOCs requires partitioning into multiple FPGAs

- Automatic partitioner processes DUT's RTL into multiple FPGAs designs

- Generates multiple Vivado project files

- Pin assignment files

- Timing constraints

- Estimates gate counts based early Vivado synthesis run data

- Flexible FPGA interconnection methods

- Direct connect using high speed IOs and cables (FMC)

- proDesign pinmux – inserts and configures proDesign pinmux IP

- Aurora chip2chip

- Verilog only

- High speed pin mux

- Supports up to ~5K signals per cable

- 64 channels x 150 pins

- up to 250 MHz channel bit rate

- Source synchronous clocking

- Ultra low skew between signals

- Supports up to ~5K signals per cable

- Partitioner adds pin mux in top-level wrapper

- User can specify clock speed and # of TDM channels

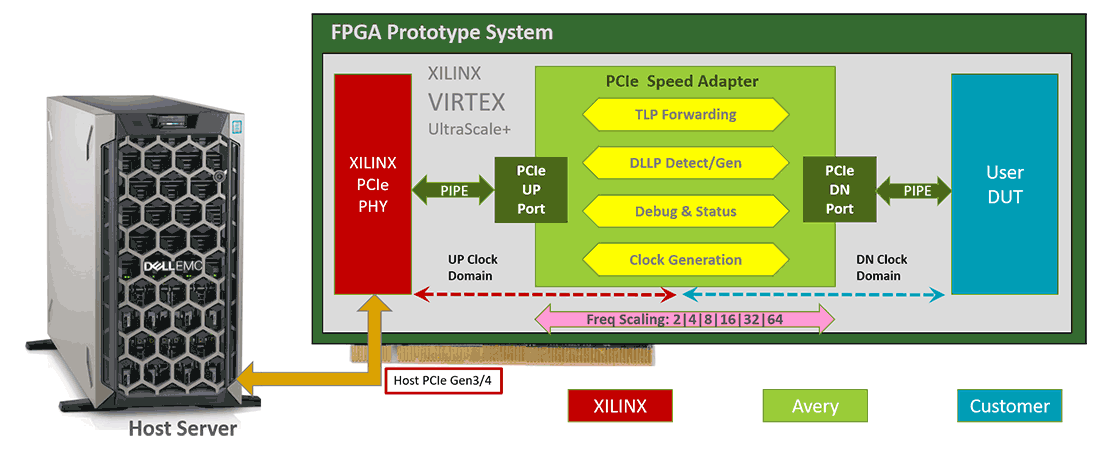

PCIe, CXL and USB Speed Adapters

- Connects an emulated PCIe Endpoint (EP) to a full speed PCIe Root Complex (RC)/host system

- The EP interface compliant with PCIe Gen3 thru Gen6

- The RC interface compliant with PCIe Gen3

- Multiple lanes of 4x, 8x, and 16x

- Supports multiple PIPE Data widths and PIPE rates

- Original mode, SERDES architecture, Low pin count interfaces

- Independent RC and EP configurations

- Ex: (EP 16x, PIPE 64bit, Gen 4.0) to (RC 4x, PIPE 32bit, Gen 3.0)

- Frequency scaling factor of emulated device down to 1/64

- Power management state of L0

- Physical layer initialization, including equalization

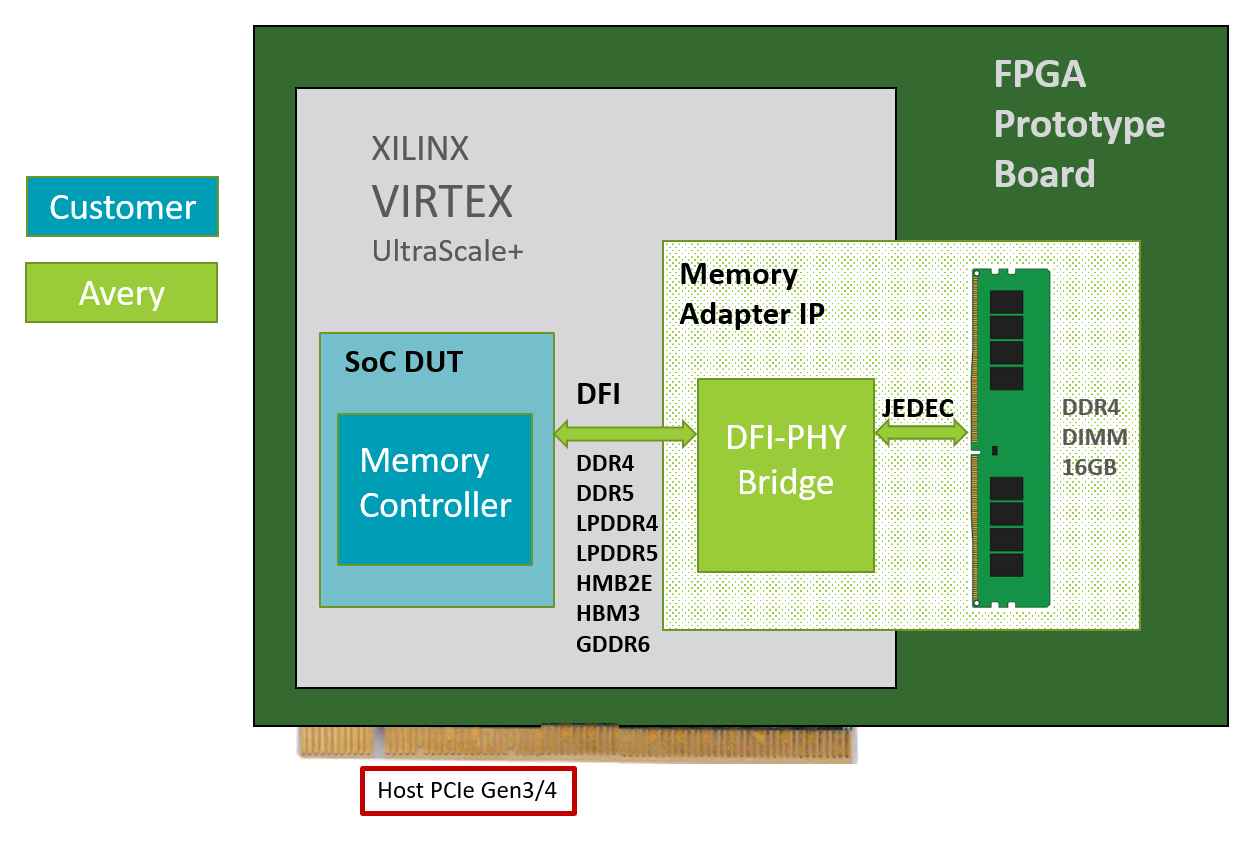

Memory Speed Adapter

- SoC DUT drives DFI interface in native DRAM interface targeted

- Supported: DDR4, DDR5, LPDDR4, HBM2E, HBM3

- Memory speed adapter converts accesses to target physical on-board memory running at native speed

- Standard FPGA boards and daughter cards