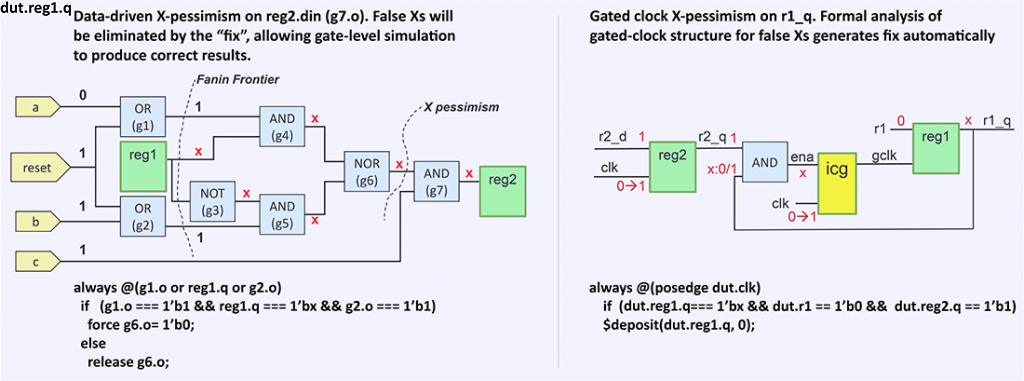

- Addressing X-pessimism in GLS is a must

- Formal-enhanced logic simulation dynamically performs X-pessimism analysis and repair on the fly

- Analyzes X propagation in datapath and gated clock logic

- False X fixes reusable on subsequent simulation runs

- Supports hierarchical flow for large designs

- Detect simulation glitches

- Dynamic glitch detectors uncover hard to find X corruption cases (0->X->1)

- Eliminate race conditions in 0-delay GLS

- 0-delay GLS may demonstrate race conditions especially in designs with gated clocking and delay lines

- “pseudo-SDF” generator efficiently solves race condition issues

- Uncover testbench forcing and connectivity issues in GLS

- Force/release propagation analysis confirms when forces no longer drive any fanout due to synthesis optimizations

- Connectivity analysis finds modules with undriven inputs creating X sources

- Complements other simulator-based X prop tools

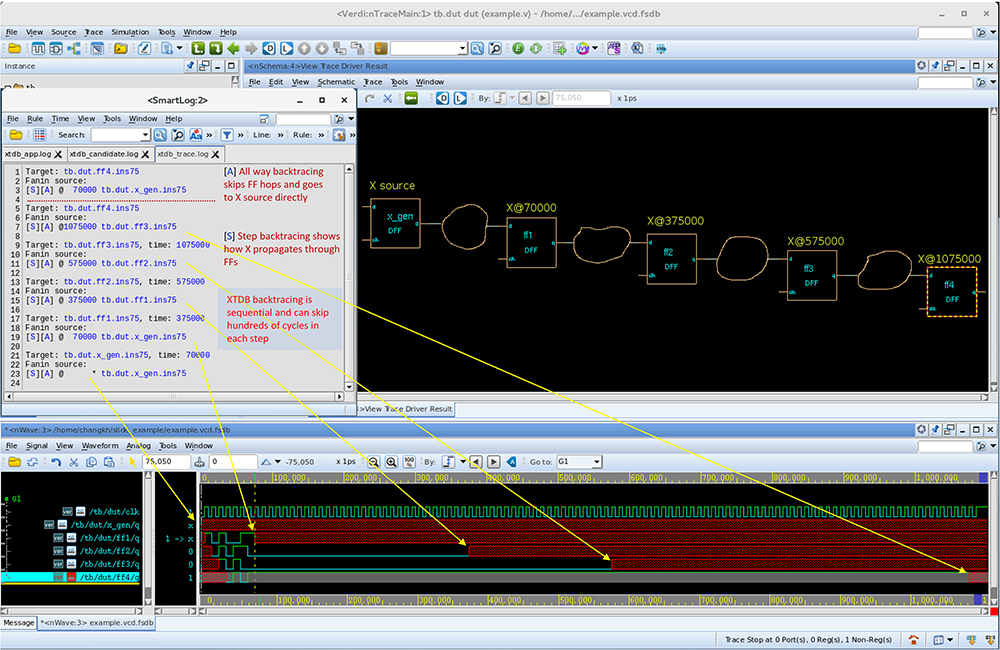

- Effectively root cause the source of real X’s

- smartlog shows X aggressors and their sequential timesteps

- Finds dynamic corruption of DFFs

- supports RTL, RTL/gate and gate-level designs

- Supports Simvision, Verdi and Questa Wave