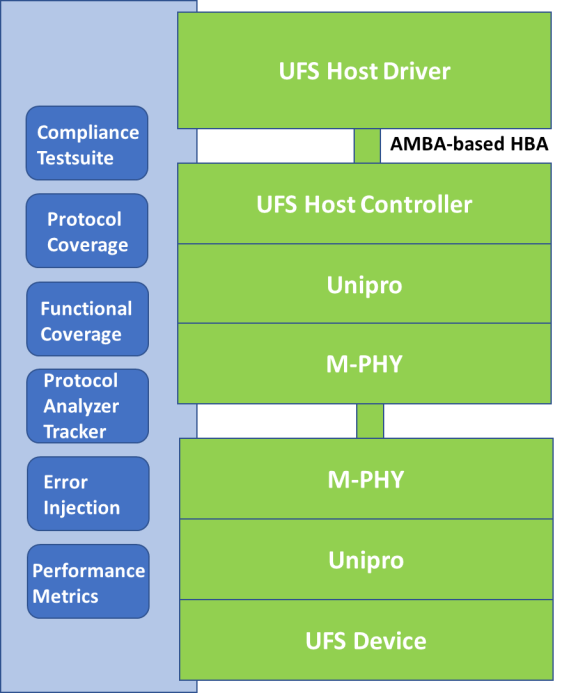

VIP for UFS Host and Device Verification support full stack and layer-level verification (UniPro or M-PHY only)

UFS VIP is a comprehensive VIP solution portfolio for UFS Host Controller (UFSHCI), UFS, and UME including MIPI UniPro and M-PHY used by SoC and IP designers to ensure comprehensive verification and protocol and timing compliance to the JEDEC standards. UFS VIP implements a complete set models, protocol checkers, and compliance testsuites in 100% native SystemVerilog and UVM.

Deliverables

- UFSHC host driver BFM

- Generic UFS host driver BFM

- UFS device BFM

- UniPro BFM

- M-PHY BFM

- Compliance testsuite

- User Guide

Features

- UFS host supported 2 ways:

- UFSHC 4.0 Driver model supports UME 1.0 and implements UFSHCI programming interface including host adapter to various host bus interfaces including AMBA AXI and AHB

- Generic Host model emulates UFSHC host driver and UFSHCI-based controller

- UFS 4.0 Device model emulates simple UFS device including sparse logical block storage and processes over 20 SCSI

- Supports command sets: Native UFS and SCSI SPC-4, SBC-3, and SAM-5

- Supports UFS DME and CPort Users

- CPort adaptor interfaces to Avery or 3rd party UniPro IP/VIP enabling mix and match between UFS and Unipro layers support module-level integration and verification

- M-PHY Model

- Support draft M-PHY 5.0

- Multiple LANE provisions

- Multiple transmission modes include LS-MODE NRZ and PWM signalling

- Multiple power saving modes

- Support Error Injections (encoding, disparity etc)

- UniPro Model

- Emulates UniPro 2.0 protocol stack layers and M-PHY

- Supports all service primitives (SAP) and service data units (x_SDU)

- DME User supports all sequences of control, configuration, and status primitives

- Transport service

- Allocates connections between CPorts

- Schedules message transfers between CPort Users

- Supports CPort signal interface

- Supports UniPro Test Feature

- Inject errors at all layers through callbacks

- Comprehensive assertions track UFS and MIPI compliance coverage

- Functional coverage tracks range of packet traffic, FSMs, and complex operational sequences

- Tracker log monitors all levels and improves debug

- Comprehensive directed and constrained random compliance testsuite for UFSHCI and UFS device achieves high protocol coverage